# МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РФ ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ «ВОРОНЕЖСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ»

# ОСНОВЫ ЦИФРОВОЙ СХЕМОТЕХНИКИ Часть 1

Основы булевой алгебры. Цифровые структуры К-типа

Учебное пособие

Составители:

В.И. Клюкин,

Ю.К. Николаенков,

Е.Н. Бормонтов

Воронеж Издательский дом ВГУ

2016

# СОДЕРЖАНИЕ

| ВВЕДЕНИЕ                                                     | 4  |

|--------------------------------------------------------------|----|

| 1. ОСНОВЫ БУЛЕВОЙ АЛГЕБРЫ                                    | 6  |

| 1.1. Логические функции и формы их представления             | 6  |

| 1.2. Минимизация логических выражений                        | 11 |

| Контрольные вопросы                                          | 14 |

| 2. ЭЛЕМЕНТНАЯ БАЗА ЦИФРОВЫХ УСТРОЙСТВ                        | 16 |

| 2.1. Основные параметры логических элементов                 | 16 |

| 2.2. ЛЭ на биполярных и полевых транзисторах                 | 19 |

| 2.3. Типы выходов цифровых элементов                         | 21 |

| 2.4. Вспомогательные элементы ЦУ                             | 24 |

| Контрольные вопросы                                          | 28 |

| 3. ФУНКЦИОНАЛЬНЫЕ УЗЛЫ КОМБИНАЦИОННОГО ТИПА                  | 30 |

| 3.1. Устройства для преобразования информации                | 31 |

| 3.2. Мультиплексоры и демультиплексоры                       | 35 |

| 3.3. Компараторы и схемы контроля                            | 37 |

| 3.4. Сумматоры                                               | 41 |

| 3.5. Арифметико-логические устройства и матричные умножители | 45 |

| 3.6. Контрольные задания по проектированию К-устройств       | 47 |

| Контрольные вопросы                                          | 49 |

| ЗАДАНИЯ ДЛЯ САМОСТОЯТЕЛЬНОГО ПРОЕКТИРОВАНИЯ                  |    |

| ЦИФРОВЫХ АВТОМАТОВ К-ТИПА                                    | 50 |

| БИБИОГРАФИЧЕСКИЙ СПИСОК                                      | 52 |

#### **ВВЕДЕНИЕ**

Информатизация общества — одна из важнейших национальных задач, требующая интенсивного развития вычислительной техники и подготовки специалистов, свободно владеющих работой на компьютере, знающих современную элементную базу цифровой и аналоговой техники и способных эффективно использовать разнообразные средства систем автоматизированного проектирования (САПР).

Основой современных систем обработки информации являются цифровые микроэлектронные устройства, постоянно укрупняющиеся и расширяющие свои функциональные возможности. Элементную базу цифровых устройств (ЦУ) составляют интегральные схемы (ИС) различного уровня сложности (оцениваемой числом базовых логических элементов), характеризующиеся высокой помехоустойчивостью и стабильностью выходных параметров. При этом все чаще используются ИС с высоким уровнем интеграции, образуя фундамент «крупноблочного» построения электронных устройств из функциональных узлов (сумматоров, мультиплексоров, счетчиков, регистров, блоков памяти, микропроцессоров), удовлетворяющих следующим требованиям:

- выполнение типовых, широко используемых функций;

- наращиваемость, т.е. возможность достаточно простого изменения числа разрядов в широких пределах;

- ограниченное число внешних связей;

- логическая, электрическая и конструктивная совместимость между собой и с сопутствующими изделиями.

«Любая дисциплина становится наукой, если в ее основу положена математика» – говорили великие философы прошлого. Научную и методическую основу схемотехники цифровых структур составляет теория логиче-

ского проектирования, использующая понятия и методы булевой алгебры (алгебры логики), вкратце (в рамках необходимого для понимания дальнейшего материала) изложенные в разделе 1. Второй раздел посвящен описанию элементной базы ЦУ, включая основные параметры логических элементов (ЛЭ), а также вспомогательные элементы ЦУ. В третьем разделе представлен материал по проектированию структурных схем ЦУ комбинационного (К-) типа с использованием карт минтермов (Карно), завершают пособие задания для самостоятельного проектирования цифровых автоматов К-типа и библиографический список.

Предлагаемое издание во многом базируется на материале учебного пособия «Логические и схемотехнические основы цифровых технологий» (2006 г.), однако за прошедшее время в такой динамичной области, как цифровая схемотехника, произошло немало изменений, особенно в разделах, связанных с программируемой логикой, запоминающими устройствами, системами синхронизации и т.п. Это не могло не быть отражено в содержании пособия, хотя ограниченность объема, лимитируемого временем на изучение излагаемого курса (~36 лекционных часов), не позволила осветить произошедшие изменения достаточно подробно. Тем не менее, рассмотренный круг вопросов (включая практические задания), может быть полезен не только студентам вузов, но и работникам научных и промышленных организаций.

## 1. ОСНОВЫ БУЛЕВОЙ АЛГЕБРЫ

Состояние входов и выходов логических элементов (ЛЭ), являющихся основой построения цифровых устройств, могут принимать только два различных значения, поэтому переменные, описывающие эти состояния, также принимают 2 значения (в цифровой технике «0» и «1»). Математика двузначных чисел есть алгебра логики, постулаты (1–5) и основные теоремы (6–13) которой представлены в табл. 1.1. где знак ( $\bullet$ ) обозначает операцию логического умножения (конъюнкцию « $\wedge$ «), а знак (+) – операцию логического сложения (дизъюнкцию « $\vee$ «). Приведенные соотношения имеют двойственный характер, т.е. могут быть получены одно из другого взаимной заменой «0»  $\leftrightarrow$  »1», (+)  $\leftrightarrow$  ( $\bullet$ ). В цифровой технике возможную двойственность устраняют понятия положительной и отрицательной логик, где в положительной логике более высокому потенциалу соответствует логическая «1», в отрицательной – логический «0».

#### 1.1. Логические функции и формы их представления

В булевой алгебре как аргументы, так и функции могут принимать только 2 значения, т.е. область определения булевых функций всегда конечна. Совокупность значений аргументов Z связана с числом переменных n соотношением  $Z=2^n$ , а число соответствующих булевых функций, обозначающих логические операции над n переменными, равно  $N_z=2^z$ . Логические функции одной и двух переменных вместе с графическими обозначениями базисных ЛЭ приведены в табл. 1.2.

Из приведенных логических операций основной базис составляют конъюнкция И, дизъюнкция ИЛИ и инверсия НЕ, образующие функционально полную систему, достаточную для реализации любой произвольно заданной функции двоичного аргумента. Примеры других функционально полных наборов ЛЭ приведены в табл. 1.3. Нетрудно заметить, что базисные логические функции И, ИЛИ, И–НЕ, ИЛИ–НЕ легко обобщаются на случай n переменных:  $f_1(x_n) = x_1 \cdot x_2 \cdot ... \cdot x_n$ ;  $f_7(x_n) = x_1 + x_2 + ... + x_n$ ;  $f_8(x_n) = \overline{x_1 \cdot x_2 \cdot ... \cdot x_n}$ . Соответствующие логические устройства (аппаратурные аналоги) будут иметь n входов.

Таблица 1.1

| N   | Аналитическое выражение                                                                                  | Примечания                     |

|-----|----------------------------------------------------------------------------------------------------------|--------------------------------|

| п/п | Timumin ioonoo baipumomio                                                                                | TIPIMIO IMIMI                  |

| 1   | $X = 0$ , если $X \neq 1$ ;                                                                              | Определение двоичной           |

|     | Х = 1, если Х ≠ 0                                                                                        | (булевой) переменной           |

| 2   | $0 \cdot 0 = 0;  1 + 1 = 1$                                                                              | Второму соотношению нет ана-   |

| 2   | 0 0 0, 1 1 1                                                                                             | лога в обычной арифметике      |

| 3   | $1 \cdot 1 = 1;  0 + 0 = 0$                                                                              |                                |

| 4   | $1 \bullet 0 = 0 \bullet 1 = 0;$                                                                         |                                |

|     | 0+1=1+0=1                                                                                                |                                |

| 5   | $\overline{0} = 1$                                                                                       | Определение операции «инвер-   |

| 3   | $\overline{1} = 0$                                                                                       | сия», «отрицание» (НЕ)         |

| 6   | $X + 0 = X;  X \cdot 1 = X$                                                                              |                                |

| 7   | $1 + X = 1;  0 \cdot X = 0$                                                                              | 1 + X + Y + = 1                |

| 8   | $X + X = X$ ; $X \cdot X = X$                                                                            | $nX = X;$ $X^n = X$            |

|     | $(\overline{X}) = \overline{X}$                                                                          | Двойная инверсия оставляет ло- |

| 9   | $\left(\overline{\overline{X}}\right) = \overline{\overline{X}} = X$                                     | гическое выражение неизменным  |

| 1.0 | $X + \overline{X} = 1$                                                                                   |                                |

| 10  | $\overline{\mathbf{X}} \bullet \mathbf{X} = 0$                                                           |                                |

| 1 1 | $X \bullet Y + X \bullet Z = X \bullet (Y + Z)$                                                          | Распределительный закон        |

| 11  | $(X+Y) \bullet (X+Z) = X + Y \bullet Z$                                                                  | Закон поглощения               |

| 12  | $\overline{X + Y + Z} + \dots = \overline{X} \bullet \overline{Y} \bullet \overline{Z} \bullet \dots$    | Таорама на Моргана             |

| 12  | $\overline{X} \cdot Y \cdot \overline{Z} \cdot \dots = \overline{X} + \overline{Y} + \overline{Z} \dots$ | Теорема де Моргана             |

|     | $f(x_1, x_2,,x_n) = x_1 f(1, x_2,,x_n) +$                                                                |                                |

|     | $+\overline{x_1} \cdot f(0,x_2,\ldots,x_n);$                                                             |                                |

| 13  | $f(x_1,x_2,,x_n) = [x_1 + f(0,x_2,,x_n)]$                                                                | Теорема разложения             |

|     | $\left[ \bullet \left[ \overline{x}_1 + f\left(1, x_2, \dots, x_n\right) \right] \right]$                |                                |

|     |                                                                                                          |                                |

Таблица 1.2

|       | Значения аргумен-<br>тов<br>X 0 0 1 1 | Аналитическое<br>выражение                                                                  | Наименование                          | Графич<br>изобра:<br>аппарат<br>анал | жение<br>урного<br>ога                  |

|-------|---------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------|-----------------------------------------|

|       | Y 0 1 0 1                             |                                                                                             |                                       | отечеств.                            | зару-<br>беж.                           |

|       | 0 0 0 0                               | $f_0 = 0$                                                                                   | Константа 0                           |                                      |                                         |

|       | 0 0 0 1                               | $f_1 = \mathbf{X} \bullet \mathbf{Y}$                                                       | Логическое умножение, конъюнкция (И)  | &                                    |                                         |

|       | 0 0 1 0                               | $f_2 = X \bullet \overline{Y}$                                                              | Запрет по Ү                           |                                      |                                         |

|       | 0 0 1 1                               | $f_3 = X$                                                                                   | Тождественность                       |                                      |                                         |

|       | 0100                                  | $f_4 = \overline{\mathbf{X}} \cdot \mathbf{Y}$                                              | Запрет по Х                           |                                      |                                         |

|       | 0101                                  | $f_5 = Y$                                                                                   | Тождественность                       |                                      |                                         |

| ции   | 0110                                  | $f_6 = \mathbf{X} \bullet \overline{\mathbf{Y}} + \overline{\mathbf{X}} \bullet \mathbf{Y}$ | Исключающее ИЛИ (неравнозначность)    | =1                                   |                                         |

| УНК   | 0111                                  | $f_7 = X + Y$                                                                               | Логическое сложение, дизъюнкция (ИЛИ) | 1                                    | <b>—</b>                                |

| фвиг  | 1000                                  | $f_8 = \overline{X + Y}$                                                                    | Стрелка Пирса<br>(ИЛИ – НЕ)           | 1                                    | <del></del>                             |

| начен | 1001                                  | $f_9 = \mathbf{X} \bullet \mathbf{Y} + \overline{\mathbf{X}} \bullet \overline{\mathbf{Y}}$ | Эквивалентность, равнозначность       | =-                                   | *************************************** |

| 31    | 1010                                  | $f_{10} = \overline{Y}$                                                                     | Инверсия Ү (НЕ)                       |                                      | =>>-                                    |

|       | 1 0 1 1                               | $f_{11} = X + \overline{Y}$                                                                 | Импликация от Y к X                   |                                      |                                         |

|       | 1100                                  | $f_{12} = \overline{X}$                                                                     | Инверсия X (НЕ)                       |                                      | <b>⇒</b>                                |

|       | 1 1 0 1                               | $f_{13} = \overline{X} + Y$                                                                 | Импликация от X к Y                   |                                      |                                         |

|       | 1110                                  | $f_{14} = \overline{\mathbf{X} \bullet \mathbf{Y}}$                                         | Штрих Шеффера<br>(И – НЕ)             | - &                                  |                                         |

|       | 1111                                  | $f_{15} = 1$                                                                                | Константа 1                           |                                      |                                         |

Таблица 1.3

| Исходный | Реализация базис                                                                                           | ных логических операций                                                                      |                |

|----------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------|

| набор ЛЭ | И                                                                                                          | или                                                                                          | HE             |

| И, НЕ    | <del></del>                                                                                                | $X+Y=\overline{\overline{X}\bullet\overline{Y}}$                                             |                |

| или, не  | $X \bullet Y = \overline{\overline{X} + \overline{Y}}$                                                     | <del></del>                                                                                  | —              |

| И – НЕ   | $X \bullet Y = \overline{\left(\overline{X \bullet Y}\right) \bullet \left(\overline{X \bullet Y}\right)}$ | $X+Y = \overline{\left(\overline{X} \cdot X\right) \cdot \left(\overline{Y} \cdot Y\right)}$ | <del>X•X</del> |

| ИЛИ – НЕ | $X \bullet Y = \overline{\left(\overline{X + X}\right) + \left(\overline{Y + Y}\right)}$                   | $X+Y = \overline{(\overline{X+Y}) + (\overline{X+Y})}$                                       | <del>X+X</del> |

Как следует из теоремы разложения (табл. 1.1, 13), любую логическую функцию n переменных можно представить в двух стандартных формах: совершенной дизъюнктивной нормальной форме (СДНФ)

$$f = \sum_{i=1}^{2^{n}-1} f_{i} m_{i}, \tag{1.1}$$

представляющей сумму минтермов  $m_i$  (произведений всех переменных, в которые каждая переменная в прямой или инверсной форме входит только один раз), и совершенной конъюнктивной нормальной форме (СКНФ)

$$f = \prod_{i=1}^{2^{n}-1} (f_i + M_i). \tag{1.2}$$

представляющей произведение макстермов  $M_i$  (сумм всех переменных, в которых каждая переменная в прямой или инверсной форме входит только один раз), где  $f_i$  = 0, 1 – коэффициенты разложения.

Совокупность минтермов и макстермов для трех аргументов приведена в табл. 1.4. Очевидно, что число минтермов (макстермов) n переменных равно  $2^n$ , а их свойства определяются соотношениями (1.3)–(1.7).

Таблица 1.4

| Значения переменных | Marriagnaria                                                                   | Момоторым М                                        | Значения      |

|---------------------|--------------------------------------------------------------------------------|----------------------------------------------------|---------------|

| XYZ                 | Минтермы $m_i$                                                                 | Макстермы $M_i$                                    | функции $f_i$ |

| 0 0 0               | $m_0 = \overline{X} \bullet \overline{Y} \bullet \overline{Z}$                 | $M_0 = \overline{X} + \overline{Y} + \overline{Z}$ | 0             |

| 0 0 1               | $m_1 = \overline{X} \cdot \overline{Y} \cdot Z$                                | $M_1 = \overline{X} + \overline{Y} + Z$            | 1             |

| 0 1 0               | $m_2 = \overline{X} \cdot Y \cdot \overline{Z}$                                | $M_2 = \overline{X} + Y + \overline{Z}$            | 0             |

| 0 1 1               | $m_3 = \overline{\mathbf{X}} \cdot \mathbf{Y} \cdot \mathbf{Z}$                | $M_3 = \overline{X} + Y + Z$                       | 0             |

| 1 0 0               | $m_4 = \mathbf{X} \bullet \overline{\mathbf{Y}} \bullet \overline{\mathbf{Z}}$ | $M_4 = X + \overline{Y} + \overline{Z}$            | 1             |

| 1 0 1               | $m_5 = X \bullet \overline{Y} \bullet Z$                                       | $M_5 = X + \overline{Y} + Z$                       | 0             |

| 1 1 0               | $m_6 = X \cdot Y \cdot \overline{Z}$                                           | $M_6 = X + Y + \overline{Z}$                       | 1             |

| 1 1 1               | $m_7 = \mathbf{X} \bullet \mathbf{Y} \bullet \mathbf{Z}$                       | $M_7 = X + Y + Z$                                  | 0             |

$$\overline{m}_i = M_{\gamma^n_{-i}}; \quad \overline{M}_i = m_{\gamma^n_{-1}};$$

(1.3)

$$\sum_{i=0}^{2^n - 1} m_i = 1; (1.4)$$

$$\prod_{i=0}^{2^n-1} M_i = 0; (1.5)$$

$$m_i m_i = 0$$

при  $i \neq j$ ; (1.6)

$$M_i + M_j = 1 \quad \text{при} \quad i \neq j. \tag{1.7}$$

Для получения СДНФ по заданной таблице истинности необходимо сложить минтермы тех наборов аргументов, для которых значения  $f_i$  булевой функции равны 1, а для получения СКНФ — перемножить макстермы наборов с  $f_i = 0$ . Действительно, для значений  $f_i$  из табл. 1.4

$$f = \begin{cases} \overline{X} \bullet \overline{Y} \bullet Z + X \bullet \overline{Y} \bullet \overline{Z} + X \bullet Y \bullet \overline{Z} & (C \square H \Phi) \\ (\overline{X} + \overline{Y} + \overline{Z}) \bullet (\overline{X} + Y + \overline{Z}) \bullet (\overline{X} + Y + Z) \bullet (X + \overline{Y} + Z) \bullet (X + Y + Z) & (C \square H \Phi). \end{cases}$$

(1.8)

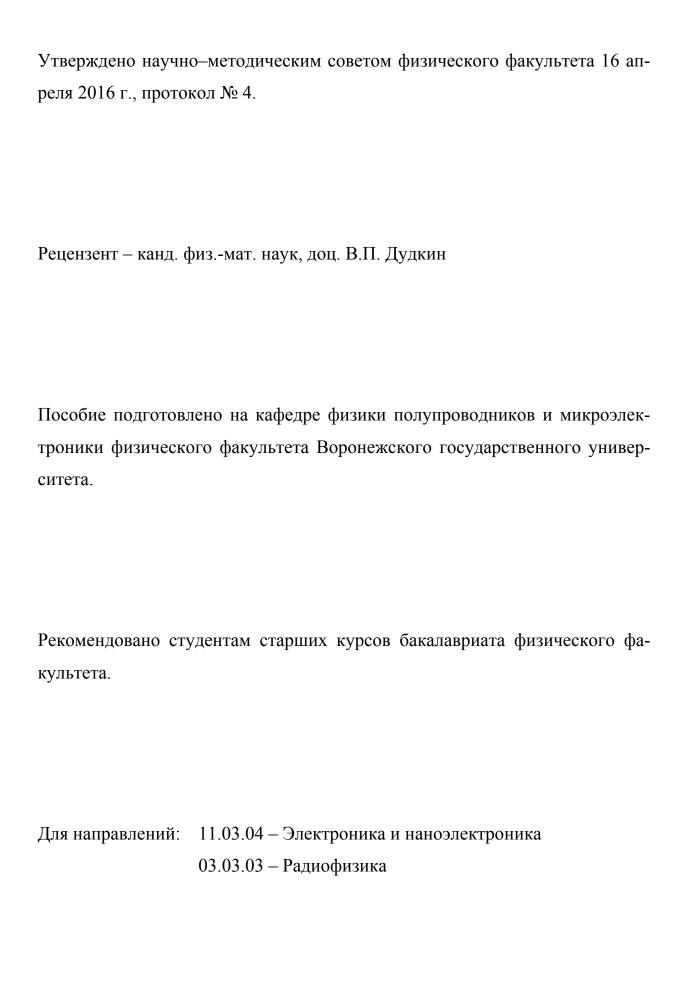

На практике удобнее пользоваться СДНФ, графически представленной коэффициентами разложения  $f_i$  на специальной карте минтермов Вейча (рис. 1.1, а — для двух переменных) или Карно (рис. 1.1, б — для трех переменных). Графическое изображение булевой функции из табл. 1.4 приведено на рис. 1.1, в (где пустые клетки карты минтермов Карно соответствуют  $f_i$  = 0).

### 1.2. Минимизация логических выражений

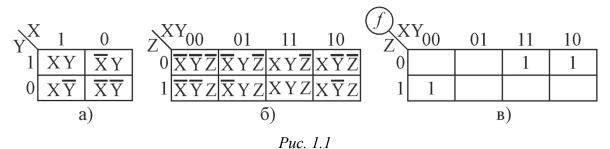

Представление булевых функций в виде стандартных СДНФ или СКНФ, удобное при преобразовании логических выражений, не всегда обеспечивает оптимальную для аппаратурной реализации форму с минимальным числом букв. Легко убедиться, что СДНФ булевой функции (1.8) допускает дальнейшее упрощение

$$f = \overline{X} \bullet \overline{Y} \bullet Z + X \bullet \overline{Y} \bullet \overline{Z} + X \bullet Y \bullet \overline{Z} = \overline{X} \bullet \overline{Y} \bullet Z + X \bullet \overline{Z},$$

(9 букв) (5 букв)

в результате которого при реализации требуется меньше базисных ЛЭ (6 вместо 7) и межсоединений (10 вместо 14) (рис. 1.2, а, б).

Puc. 1.2

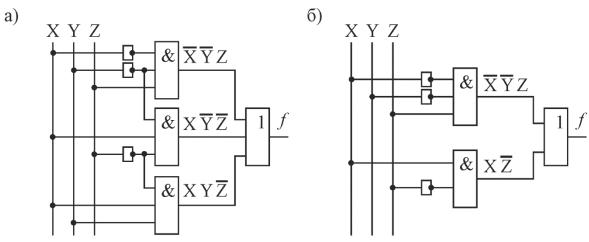

Наиболее удобен метод упрощения, основанный на «склеивании» (объединении) минтермов СДНФ булевой функции, графически представленной в виде карты Карно (типа рис. 1.1, в). Правила «склеивания» минтермов следующие:

- допускают объединение  $2^m$  минтермов, расположенных в соседних строках (столбцах) карты Карно;

- соседними строками (столбцами) считаются такие, при переходах между которыми изменяет свое значение только одна переменная;

- полученное в результате объединения минтермов выражение содержит на m букв меньше, чем любой из исходных минтермов;

- в конечном выражении пропадают те переменные, которые при переходах между объединяемыми минтермами изменяют свое значение;

- один и тот же минтерм может быть использован для «склеивания» неограниченное число раз.

Примеры упрощения булевых функций трех и четырех аргументов с помощью «склеивания» минтермов приведены на рис. 1.3.

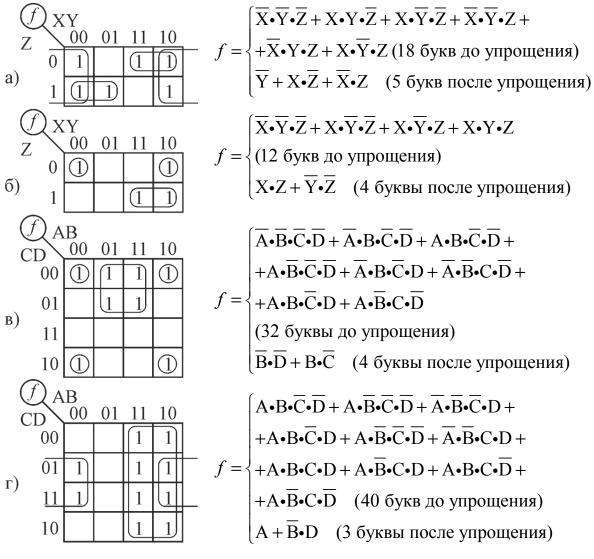

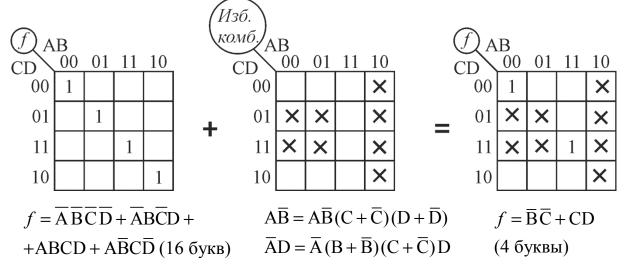

В логическом проектировании цифровых устройств часто случается так, что при работе схем некоторые комбинации значений переменных никогда не должны появляться. Такие комбинации называют избыточными (нештатными), в картах минтермов их обозначают крестиком, при упрощении булевых функций их используют для «склеивания» минтермов путем доопределения, т.е. превращения (по желанию) крестика в 0 или 1. Пример упрощения логической функции  $f = \overline{A} \, \overline{B} \, \overline{C} \, \overline{D} + \overline{A} \, \overline{B} \, \overline{C} \, \overline{D}$ , когда избыточными комбинациями выступают  $\overline{AB}$  и  $\overline{AD}$ , приведен на рис. 1.4.

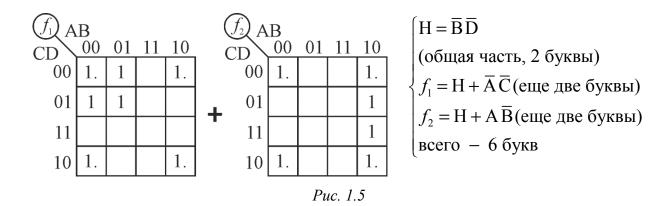

Обычно функционирование цифрового устройства описывается большим количеством логических функций, в которых встречаются повторяющиеся комбинации минтермов. Это может быть использовано для совместного упрощения системы булевых выражений путем выделения общей для всех функций части с помощью карт минтермов.

Puc. 1.3

Puc. 1.4

Пример минимизации системы логических функций

$$\begin{cases} f_1 = \overline{A}\overline{C} + A\overline{B}\overline{C}\overline{D} + \overline{B}C\overline{D}; & \text{BCEFO} \\ f_2 = \overline{B}\overline{D} + A\overline{B}D & \text{14 букв} \end{cases}$$

приведен на рис 1.5, где в картах Карно точками отмечены одинаковые для обеих функций минтермы, образующие общую часть  $H = \overline{BD}$ . Видно, что указанной процедурой удалось значительно снизить цену рассматриваемой системы (с 14 до 6 букв).

#### Контрольные вопросы

- 1. Почему все выражения алгебры логики имеют двойственный характер?

- 2. Чем отличаются постулаты булевой алгебры от постулатов обычной арифметики?

- 3. Что происходит с логическим выражением при его двойной инверсии?

- 4. Покажите справедливость закона поглощения (X+Y)(X+Z) = X+YZ для булевых переменных.

- 5. Какое количество логических функций можно реализовать для n булевых переменных?

- 6. Что такое функционально полная система базисных логических функций? Приведите примеры.

- 7. Покажите справедливость соотношения  $\overline{A \oplus B} = AB + \overline{AB}$ .

- 8. Докажите, что сочетание базовых ЛЭ ИСКЛЮЧИТЕЛЬНОЕ ИЛИ, И, «1» образует функционально полную систему.

- 9. Каков конечный результат последовательного применения теоремы разложения к булевой функции n переменных?

- 10. Как получить СДНФ и СКНФ булевой функции из её таблицы истинности?

- 11. Сколько клеток на карте минтермов занимает минтерм? макстерм?

- 12. Каковы правила объединения («склеивания») минтермов при упрощении булевых функций?

- 13. Как используются нештатные (избыточные) комбинации при упрощении логических выражений?

- 14. Определите процедуру минимизации нескольких булевых функций одновременно.

- 15. Выполните минимизацию булевой функции f(A,B,C,D) при наличии избыточных комбинаций  $\varphi(A,B,C,D)$ :

a)

$$f(A,B,C,D) = \overline{A} \overline{B} \overline{C} + \overline{A} B D + A B C + A \overline{B} C \overline{D};$$

$\varphi(A,B,C,D) = \overline{A} \overline{B} C D, \overline{A} B \overline{C} \overline{D}, A B C \overline{D} и A \overline{C} D;$

$$δ) f(A,B,C,D)=\overline{A} \overline{B} \overline{C} \overline{D}+\overline{A} \overline{B} \overline{C} D+A \overline{B} C D+A \overline{B} C \overline{D};$$

$$φ(A,B,C,D)=\overline{A} \overline{B} C \overline{D}, \overline{A} \overline{B} C D, \overline{A} \overline{C}.$$

16. Какое минимальное количество букв имеет система булевых функций:

a)

$$\begin{cases} f_1 = \overline{A} \ \overline{B} \ \overline{C} + \overline{A} \ \overline{B} \ C + A \ \overline{C} \ \overline{D} + A \ C \ \overline{D}; \\ f_2 = \overline{A} \ \overline{B} \ \overline{D} + A \ \overline{B} \ \overline{D} + A \ B \ D; \end{cases}$$

6)

$$\begin{cases} f_1 = A B + \overline{C} D + \overline{A} B C D; \\ f_2 = B D + \overline{A} B \overline{D} + \overline{B} C D. \end{cases}$$

17. В каких случаях при аппаратной реализации цифровых устройств предпочтительнее использовать СДНФ, а в каких – ДНФ выходных логических выражений?

## 2. ЭЛЕМЕНТНАЯ БАЗА ЦИФРОВЫХ УСТРОЙСТВ

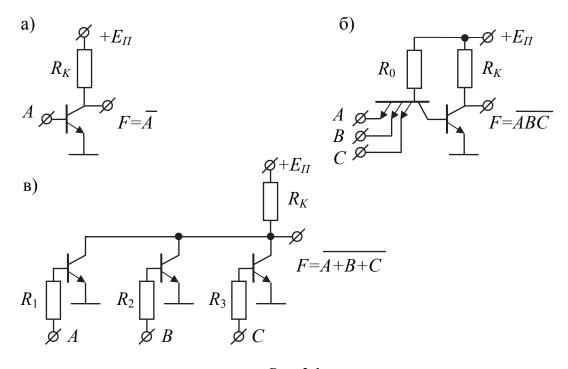

В основе любого ЛЭ лежит управляемая ключевая цепь (реле) с двумя устойчивыми состояниями. Примеры реализации базовых элементов НЕ, И—НЕ, ИЛИ—НЕ на основе транзисторного биполярного ключа ОЭ (с общим эмиттером) приведены на рис. 2.1 а, б, в соответственно. Далее, выходные показатели ЦУ будут определяться их элементной базой, т.е. параметрами входящих в них ЛЭ. Ясно, что для правильного проектирования и эксплуатации ЦУ необходимо знать эти параметры.

Puc. 2.1

#### 2.1. Основные параметры логических элементов

Наиболее значимыми характеристиками ИС ЛЭ являются следующие:

- *напряжение питания*  $U_n$  (вместе с полем допуска);

- уровень логической единицы  $U^1$  (аналогично);

- уровень логического нуля  $U^0$  (аналогично);

- потребляемая мощность

$$P = P_{cm} + P_{\partial uH}, \tag{2.1}$$

где  $P_{cm} = \frac{1}{2} \left( P_{cm}^0 + P_{cm}^1 \right)$  — мощность, потребляемая в статическом режиме;  $P_{cm}^0, P_{cm}^1$  — потребляемая мощность в состояниях логического «0» и логической «1» соответственно;  $P_{\partial u H} = C_H U_J^2 f_p$  — мощность, потребляемая в динамическом режиме;  $C_H$  — емкость нагрузки;  $U_J = U^1 + U^0$  — логический перепад;  $f_p$  — рабочая частота (переключений ЛЭ);

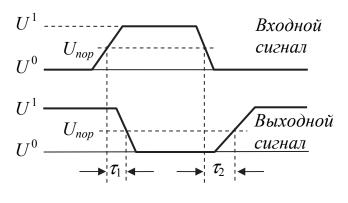

• быстродействие, определяемое временем задержки распространения сигнала

$$\tau_3 = \frac{\tau_1 + \tau_2}{2},\tag{2.2}$$

где  $au_1$  – время запаздывания фронта включения;  $au_2$  – время запаздывания фронта выключения (рис. 2.2);  $U_{nop} = \frac{1}{2} \left( U^1 + U^0 \right)$ . Заметим, что определение

Puc. 2.2

### (2.2) не относится к технологическому разбросу задержек:

• работа (энергия) единичного переключения

$$A = P\tau_3, \tag{2.3}$$

характеризующая физико-технологический и схемотехнический уровень разработки ИС ЛЭ. Действительно, поскольку  $P \sim \frac{E_{II}^2}{R_{\odot}}, \tau_3 \sim R_{\odot}C_{\odot}, C_{\odot} \sim ab$ ,

то  $A \sim E_{\Pi}^2 ab$ , где a, b — линейные размеры активных элементов ЛЭ, определяемые разрешающей способностью литографии, используемой при изготовлении ИС;

- *помехоустойчивость*, определяемая допустимыми уровнями динамической  $U^{\Pi}_{\partial u n}$  или (чаще всего) статической  $U^{\Pi}_{cm}$  помехи, которая может изменить состояние ЛЭ;

- коэффициент объединения по входу  $K_{ob}$  число логических входов ЛЭ;

- коэ $\phi$ фициент разветвления по выходу  $K_{pазв}$  допустимое число подключаемых к выходу нагрузок, под которыми понимаются входы таких же ЛЭ.

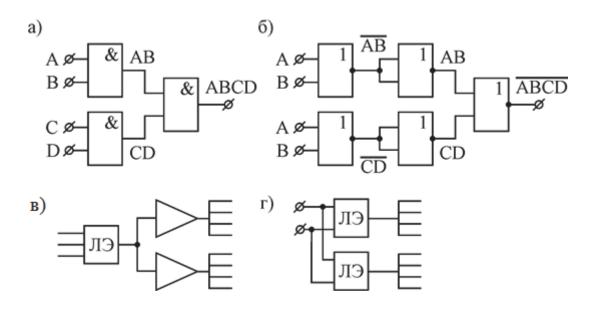

Увеличение  $K_{paз6}$  ограничено максимальным рабочим током ЛЭ, разбросом их параметров, а также увеличением суммарной емкости нагрузки  $C_H$ , приводящей к росту P и  $\tau_3$ . При необходимости увеличения  $K_{o6}$  и  $K_{pas6}$  к ЛЭ подключают дополнительные элементы (ЛЭ или буферные каскады), обеспечивающие *расширение по входу* (рис. 2.3, а, б) или *по выходу* (рис. 2.3, в, г).

Puc. 2.3

#### 2.2. ЛЭ на биполярных и полевых транзисторах

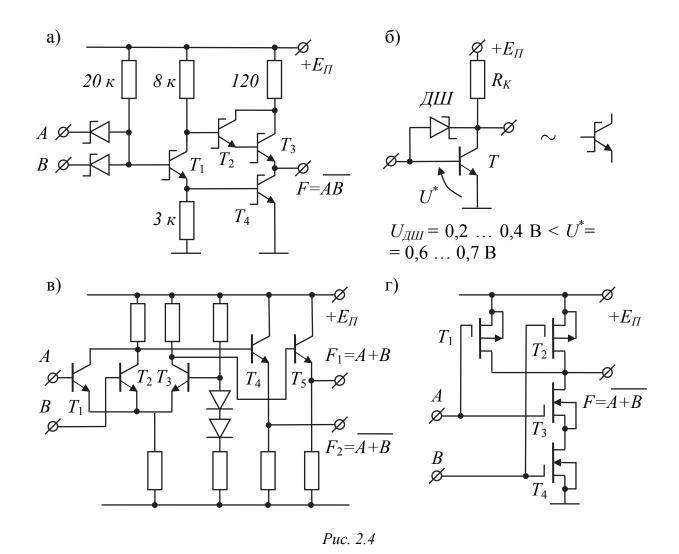

Исторически первыми были ИС ЛЭ на основе диодной, диодно-(ДТЛ), транзисторной транзисторно-транзисторной (ТТЛ) логики (рис. 2.1, б), а также транзисторной логики с непосредственными связями (ТЛНС, рис. 2.1, в), выполненные на биполярных транзисторах. С разработкой полевых структур они были дополнены МОП-, КМОП- и БиКМОПлогикой. Современные цифровые технологии ориентированы на использование КМОП- (для внутренних узлов ЦУ), ТТЛ(Ш)- (ТТЛ с барьером Шоттки, для интерфейсных и периферийных узлов, где необходимы достаточно большие рабочие токи) и ЭСЛ- (эмиттерно-связанной, для сверхбыстродействующих БИС/СБИС) логики. Принципиальные схемы типичных представителей семейств ТТЛ(Ш)-, ЭСЛ- и КМОП- ИС ЛЭ приведены на рис. 2.4, а, в, г соответственно. Рис. 2.4, б поясняет функционирование биполярного транзистора с диодом Шоттки (ДШ), в котором благодаря отрицательной обратной связи (ОС) коллектор-база через ДШ отсутствует режим насыщения. Также без насыщения работает переключатель тока ЭСЛ (Т2, Т3, рис. 2.4, в), что обеспечивает ЛЭ ТТЛ(Ш) и ЭСЛ высокое быстродействие (рабочая частота элементов ТТЛ(Ш) достигает 500 МГц, а элементов ЭСЛ – 2.0 ГГц).

Типичные параметры наиболее распространенных семейств транзисторных логик приведены в табл. 2.1, где для всех типов ЛЭ номинальная величина напряжения питания  $\left|E_{\Pi}^{\scriptscriptstyle{HOM}}\right| \approx 5$  В. Видно, что из стандартных логик максимальным быстродействием обладают ЭСЛ-схемы, а наиболее экономичны и помехоустойчивы КМОП-структуры. Особое положение занимают ЛЭ МЕП (структуры металл—полупроводник на подложке из арсенида галлия GaAs), работающие на тактовых частотах до 5 ГГц, имеющие невысокую мощность потребления, хотя и более дорогие в изготовлении. Наряду с ЭСЛ-схемами они получили распространение в сверхскоростных блоках БИС/СБИС типа «система на кристалле».

Таблица 2.1

| Тип    | $U_{\scriptscriptstyle HOM}^1$ | $U_{\scriptscriptstyle HOM}^0$ | $P_{cm}$ | $	au_{3cp}$ | $f_{max}$ | $A_{cp}$ | $U_{\it cm}^{\it \Pi}$ | $K_{o\delta}$  |

|--------|--------------------------------|--------------------------------|----------|-------------|-----------|----------|------------------------|----------------|

| логики | (B)                            | (B)                            | (мВт/ЛЭ) | (нс)        | (МГц)     | (пДж)    | (B)                    | $K_{\it pa36}$ |

| ТТЛ(Ш) | ~ 5                            | ~ 0,3                          | 1,010    | 15          | 200       | 1020     | 0,8                    | 5/10           |

| КМОП   | ~ 5                            | ~ 0,1                          | 0,010,1  | 520         | 100       | 15       | 1,52,0                 | 5/100          |

| ЭСЛ    | 0,8                            | 1,7                            | 2050     | 0,51,0      | 1000      | 1020     | 0,3                    | 5/20           |

| МЕП    | ~ 5                            | ~ 0,2                          | 0,10,5   | 0,150,5     | 4700      | 0,10,5   | 0,5                    | 5/10           |

В заключение упомянем о некоторых проблемах, связанных с использованием ТТЛ(Ш) и КМОП-логик при построении ЦУ. Биполярные ТТЛ(Ш)-элементы предъявляют высокие требования к источнику питания (5 В ± 5% при относительно высокой мощности рассеяния) и весьма чувствительны к помехам типа всплесков по шине земли. Входы КМОП-схем имеют очень большой разброс по значениям порогового напряжения, что в сочетании с высоким выходным импедансом (200–500 Ом) приводит к скосу фронтов тактовых импульсов и ложным срабатываниям. Поэтому в устройствах на КМОП-логике все неиспользуемые входы должны обязательно быть соединены с шинами питания или земли. Это требование, вообще говоря, справедливо и для ЛЭ ТТЛ(Ш), ибо в противном случае страдают параметры быстродействия элементов. Кроме того, выходы КМОП-элементов подвержены пробою под действием статического электричества, так что при работе с этими ЛЭ следует соблюдать особую осторожность.

#### 2.3. Типы выходов цифровых элементов

Цифровые элементы (логические, запоминающие, буферные) могут иметь выходы следующих типов: логические, с третьим состоянием, с открытым коллектором (стоком), с открытым эмиттером (истоком), что объясняется различными условиями работы ЛЭ в логических цепях, магистрально-модульных системах и т.д.

*Логический выход* формирует 2 уровня выходного напряжения ( $U^0$  и  $U^1$ ), его выходное сопротивление стремятся сделать малым, способным развивать большие токи для перезаряда емкостных нагрузок, и, следовательно, получения высокого быстродействия ЛЭ. Схемы логических выходов элементов ТТЛ(Ш) и КМОП ( $T_2$ ,  $T_3$ ,  $T_4$  рис. 2.4, а,  $T_1$ – $T_3$ ,  $T_2$ – $T_4$  рис. 2.4, г) аналогичны двухтактным каскадам – в них оба фронта выходного напряжения формируются активным режимом транзисторов, работающих противофазно, что обеспе-

чивает малое  $R_{\text{вых}}$  при любом направлении переключения. Первая особенность таких выходов — их нельзя соединять параллельно из-за возможной логической неопределенности и заметных уравнительных токах при переключениях, вторая — создание импульсных токовых помех в цепях питания при переходных процессах из-за некоторой несинхронности переключения транзисторов, что порождает короткий импульс сквозного тока значительной величины.

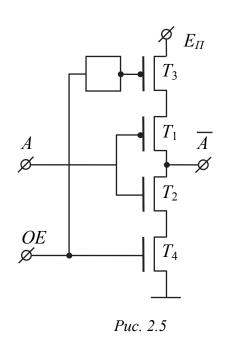

Элементы с тремя состояниями (TC) выхода кроме логических «0» и «1» имеют состояние «отключено», в котором ток выходной цепи пренебрежимо мал. В это состояние ЛЭ переводится специальным управляющим сиг-

налом ОЕ (Output Enable), обеспечивающим запертое состояние обоих транзисторов двухтактного выхода. На рис. 2.5 показан выходной каскад инвертора с ТС, используемый в схемотехнике КМОП. Видно, что при наличии разрешения (OE=1) транзисторы  $T_3$ ,  $T_4$  открыты и инвертор выполняет свою логическую операцию, при его отсутствии (OE=0) выход инвертора переходит в состояние «отключено». Буферные элементы с ТС широко используются в ЦУ для управляемой передачи сигналов по тем или иным линиям.

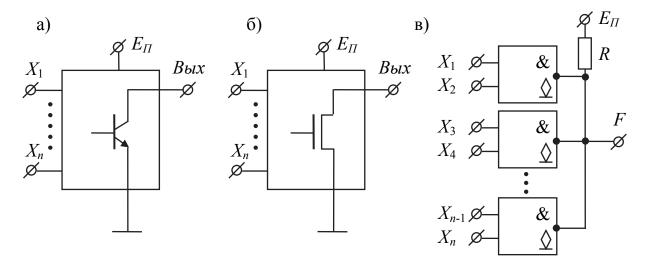

Элементы с открытым коллектором (OK) или стоком (OC) имеют выходную цепь, заканчивающуюся одиночным транзистором, коллектор (сток) которого не соединен с какими-либо цепями внутри ИС (рис. 2.6, а, б). От предыдущей части схемы транзисторы управляются так, что могут находиться в насыщенном (для МОП-транзистора просто открытом) или запертом состоянии, которые трактуются как отображение «0» или «1» соответственно, хотя для получения  $U^1$  требуется подключение нагрузки. Несколько

Puc. 2.6

выходов ОК (ОС) можно соединять параллельно, подключая их к общей для всех выходов цепи  $E_{\Pi}$ –R (рис. 2.6, в). При этом возможна реализация режима поочередной работы ЛЭ на общую линию (аналогично элементам с ТС) или дополнительной логической операции, называемой операцией *монтажной логики*. Так, например, для комбинации ЛЭ на рис. 2.6, в

$$F = \overline{X_1 X_2} \bullet \overline{X_3 X_4} \bullet \dots \bullet \overline{X_{n-1} X_n} = \overline{X_1 X_2 + X_3 X_4 + \dots + X_{n-1} X_n}.$$

В обозначениях элементов с ОК или ОС после символа функции ставится ромб с черточкой снизу.

Положительной чертой ЛЭ с ОК (ОС) при работе в магистрально—модульных системах является их защищенность от повреждений при ошиб-ках управления, недостатком — большая задержка переключения из «0» в «1», когда выходная емкость заряжается сравнительно малым током резистора R.

Выход с открытым эмиттером характерен для элементов ЭСЛ (транзисторы  $T_4$ ,  $T_5$  рис. 2.4, в). Соединение этих выходов (для различных ЛЭ) друг с другом приводит к получению дополнительной операции монтажной логики ИЛИ (при объединении прямых выходов ЛЭ) или И–ИЛИ (при объединении инверсных). Например, для второго случая имеем

$$F = \overline{X_1 + X_2} + \overline{X_3 + X_4} = \overline{X_1} \ \overline{X_2} + \overline{X_3} \ \overline{X_4}.$$

#### 2.4. Вспомогательные элементы ЦУ

К числу вспомогательных относятся элементы, не выполняющие логических операций или запоминания данных, но очень часто необходимые для построения ЦУ: элементы задержки, формирования и генерации импульсных сигналов, а также их визуальной индикации.

Задержка цифровых сигналов требуется для временного согласования их распространения по различным путям в ЦУ с целью предотвращения ложных срабатываний автоматов с памятью. Варианты технической реализации линий задержки (ЛЗ) весьма различны: отрезки кабелей, цепочки ЛЭ, искусственные электромагнитные ЛЗ, RC-цепи, одновибраторы, схемы деления частоты тактовых импульсов. Наиболее типичными для ЦУ являются цепочки ЛЭ и RC-цепочки. В первом случае используется естественная инерционность ЛЭ, т.е. общее время задержки  $\tau_3$  определяется как  $\tau_3 = \sum_{i=1}^n \tau_{3i}$ , где  $\tau_{3i}$  – задержки отдельных элементов. Задержку на большее время (до единиц миллисекунд) получают с помощью RC-цепей в трактах передачи сигналов ( $\tau_3 \approx 0.7$ RC), причем их можно использовать как непосредственно (обеспечивая условия согласования), так и в форме времязадающих цепей одновибраторов. Нередко для задержки сигналов в ЦУ используют счетчики, с помощью которых получают  $\tau_3 = MT$ , где M – емкость счетчика, T – период тактовых синхроимпульсов.

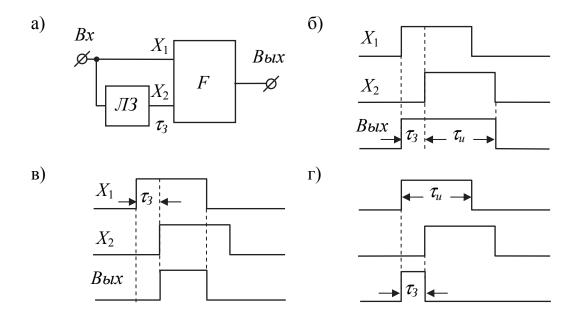

К задачам формирования импульсов относятся расширение, сужение и стандартизация их длительности. Реализация этих операций осуществляется схемой рис. 2.7, а при  $F = X_1 + X_2$  (рис. 2.7, б),  $F = X_1 X_2$  (рис. 2.7, в) и  $F = X_1 \overline{X_2}$  (рис. 2.7, г) соответственно.

Puc 2.7

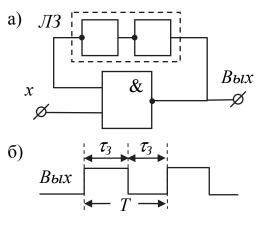

Генераторы импульсных последовательностей строятся на основе логических элементов и ЛЗ. Простейший вариант генератора симметричных импульсов приведен на рис. 2.8, где элемент задержки ЛЗ в цепи обратной связи (ОС) И–НЕ образован двумя инверторами НЕ. При  $U_{ex}$  = «0» на выходе и, соответственно, верхнем входе И–НЕ присутствует потенциал «1». Перевод  $U_{ex} \rightarrow$  »1» является командой для начала работы генератора. Выход И–НЕ переходит в состояние «0», которое через время  $\tau_3$  появится на верхнем входе И–НЕ, переводя  $U_{eux} \rightarrow$  »1», которая через время  $\tau_3$  появится на

Puc. 2.8

верхнем входе И–НЕ, и т.д. Генераторами прямоугольных импульсов служат также типовые схемы мультивибраторов, стабильность частоты которых аналогична генераторам с ЛЗ (порядка  $10^{-4}$  град $^{-1}$ ). Для получения тактовых импульсов с высокой стабильностью частоты ( $10^{-6}$ – $10^{-7}$  град $^{-1}$ ) применяют генераторы с кварцевыми резонаторами.

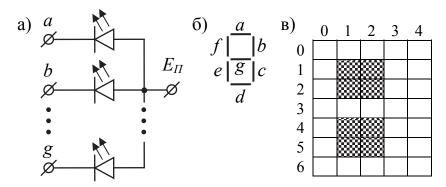

Для общения с оператором ЦУ снабжаются средствами визуального представления данных: световыми индикаторами, матрицами и экранными дисплеями. Преобразование электрических сигналов в видимое изображение может быть основано на разных физических явлениях: светоизлучении полупроводниковых структур, оптических явлениях в жидких кристаллах, электролюминесценции, свечении газовых разрядов. До недавнего времени основой средств визуализации служили светодиоды на основе полупроводниковых материалов (арсенида галлия, фосфида галлия), пропускание тока через которые (~5–10 мА при  $U_{\theta} \approx 1$ –2 В) вызывает их свечение. Из них составляются индикаторы или матрицы (рис. 2.9), отображающие буквы или цифры. Для отображения цифр чаще используют семисегментные индикаторы (ССИ), в которых семь сегментов – диодов (рис. 2.9, а) расположены так (рис. 2.9, б), что при зажигании определенной их комбинации высвечивается тот или иной символ. Логическое управление ССИ осуществляют стандартными ИС-дешифраторами согласно таблице истинности табл. 2.2, где цифры десятичного кода (ДК) представлены двоичными комбинациями четырехразрядного ( $A_0B_0C_0D_0$ ) бинарного кода (БК). Отображение букв и цифр осуществляют индикаторными матрицами (пример неполной матрицы с исключенными неиспользуемыми сегментами приведен на рис. 2.9, в), где управление сегментами производится аналогично ССИ. Матрицы с большим числом сегментов образуют плоские дисплеи.

Puc. 2.9

Таблица 2.2

| ДК | БК             |   | - | Возбужд | ающие с | сегменть | I |   |

|----|----------------|---|---|---------|---------|----------|---|---|

| ДК | $A_0B_0C_0D_0$ | а | b | С       | d       | e        | f | g |

| 0  | 0000           | 1 | 1 | 1       | 1       | 1        | 1 | 0 |

| 1  | 0001           | 0 | 1 | 1       | 0       | 0        | 0 | 0 |

| 2  | 0010           | 1 | 1 | 0       | 1       | 1        | 0 | 1 |

| 3  | 0011           | 1 | 1 | 1       | 1       | 0        | 0 | 1 |

| 4  | 0100           | 0 | 1 | 1       | 0       | 0        | 1 | 1 |

| 5  | 0101           | 1 | 0 | 1       | 1       | 0        | 1 | 1 |

| 6  | 0110           | 1 | 0 | 1       | 1       | 1        | 1 | 1 |

| 7  | 0111           | 1 | 1 | 1       | 0       | 0        | 0 | 0 |

| 8  | 1000           | 1 | 1 | 1       | 1       | 1        | 1 | 1 |

| 9  | 1001           | 1 | 1 | 1       | 1       | 0        | 1 | 1 |

Второй тип индикаторов с обычным для ИС уровнями управляющих сигналов — жидкокристаллические индикаторы (ЖКИ), молекулы веществ которых под действием электрического поля могут приобретать упорядоченную ориентацию в пространстве, что изменяет их оптические свойства. Основное достоинство ЖКИ — высокая энергетическая экономичность (токи управления  $\sim 10$  мкА при  $E_{II} \sim$  нескольких В), что обусловило их широкое применение, прежде всего для портативных компьютеров. Заметим, однако, что управляющее напряжение ЖКИ не должно содержать постоянной составляющей, иначе они очень быстро выйдут из строя. Поэтому в ЦУ для возбуждения сегментов ЖКИ используют прямоугольные импульсы с тактовой частотой в 70, ..., 100  $\Gamma$ ц, при которой вследствие инерционности зрения мелькание сегментов не ощущается.

#### Контрольные вопросы

- 1. Что такое ЛЭ с положительной (отрицательной) логикой в цифровой схемотехнике?

- 2. На основе какого единственного элемента может быть построено любое цифровое устройство?

- 3. Какие основные параметры ЛЭ Вы знаете?

- 4. Как определяется мощность, потребляемая ЛЭ в статическом режиме? Почему?

- 5. Какую информацию о реализации ЛЭ дает работа (энергия) единичного переключения?

- 6. Каковы методы расширения ЛЭ по входу? по выходу?

- 7. Какие типы логик имеют преимущественное использование во внутренних и внешних узлах ЦУ?

- 8. Как осуществляется механизм повышения быстродействия в биполярной логике ТТЛШ?

- 9. Почему ЛЭ ЭСЛ имеют высокое быстродействие? За счет чего оно достигается? Почему  $f_p$  ЭСЛ-логики превышает  $f_p$  логики ТТЛШ?

- 10. Чем обусловлено максимальное быстродействие ЛЭ биполярных логик на основе GaAs?

- 11. Какова основная причина низкого потребления КМОП-логики?

- 12. Почему ЛЭ на МДП-транзисторах имеют высокую помехоустойчивость?

- 13. Как поступают с неиспользуемыми входами в КМОП-логике и почему? Следует ли при этом учитывать тип ЛЭ?

- 14. Почему в ЛЭ ТТЛ(Ш)- и КМОП-логик применяют 2-тактные выходные каскады? Каковы особенности функционирования таких выходов?

- 15. Какие типы выходов ЛЭ используются при построении цифровых устройств?

- 16. Где используются ЛЭ с тремя состояниями выхода?

- 17. Как реализуется операция монтажной логики? Какие типы выходов ЛЭ допускают ее осуществление?

- 18. Назовите основные вспомогательные элементы, используемые при технической реализации ЦУ?

- 19. Назовите основные способы реализации элементов задержки в ЦУ? Зачем они необходимы?

- 20. Каким образом осуществляется расширение, сужение и стандартизация длительности импульсных сигналов в ЦУ?

- 21. Приведите схему генератора импульсов с ЛЗ и поясните принцип ее работы.

- 22. Расскажите о средствах визуального представления данных в ЦУ, их достоинствах и недостатках.

# 3. ФУНКЦИОНАЛЬНЫЕ УЗЛЫ КОМБИНАЦИОННОГО ТИПА

Любое ЦУ состоит из типовых функциональных узлов и некоторого количества логических схем, специальных для данного конкретного проекта. Функциональные узлы, как и все ЦУ вообще, делятся на комбинационные (однотактные автоматы без запоминания) и последовательностные (автоматы с памятью), различие между которыми имеет фундаментальный характер. Для комбинационной схемы (К-типа) состояние выходов (функций) определяется только текущим значением входов (аргументов), предыстория значения не имеет, для последовательностной (П-типа) — значения выходных величин зависят не только от состояния входов в данный момент времени, но и от состояния выходов на предыдущем такте. Для схем К-типа характерно отсутствие обратных связей, для схем П-типа — их наличие.

Номенклатура схем К-типа включает базовые ЛЭ (И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ), а также различного рода сумматоры, шифраторы, мультиплексоры, дешифраторы, преобразователи кодов, компараторы, схемы свертки, арифметико-логические устройства (АЛУ), блоки ускоренного переноса и матричные умножители. Проектирование логических К-схем обычно состоит из трех этапов:

- 1) по логическому (словесному) описанию решаемой задачи строится таблица истинности со всеми возможными комбинациями входных и соответствующими значениями выходных переменных;

- 2) с помощью карт минтермов определяются СДНФ (при реализации на табличных логических блоках) или ДНФ (с минимизацией СДНФ при реализации на основе базовых ЛЭ) выходных логических функций;

- 3) с учетом выбранной элементной базы реализуется структурная, а затем и принципиальная схема проектируемого ЦУ.

#### 3.1. Устройства для преобразования информации

Поскольку ЛЭ реализуют только два устойчивых состояния, любая обрабатываемая ЦУ информация должна быть представлена в бинарной форме. Схемы, преобразующие информацию к двоичному виду, называют шифраторами (Ш), для обратных преобразований служат дешифраторы (ДШ), переходы между различными двоичными представлениями осуществляют преобразователи кодов (ПК). Простейшими кодами для записи цифровой информации являются четырехэлементные коды, каждое слово которых содержит четыре двоичных цифры. Общее число всех возможных четырехэлементных кодов велико ( $\sim 3\cdot 10^{10}$ ), однако чаще всего используют весовые, циклические и самодополняющиеся коды. Некоторые из наиболее употребительных кодов для представления десятичных цифр приведены в табл. 3.1, где БК (бинарный код) – весовой двоичный код прямого замещения, код Грея – равнодистантный циклический код, код+3 (код с избытком 3) – самодополняющийся код, образующийся из БК прибавлением двоичного эквивалента 3 (0011), код Айкена – самодополняющийся весовой код, код 2 из 5 – позволяет обнаруживать все единичные ошибки, код Джонсона – «регистровый» код.

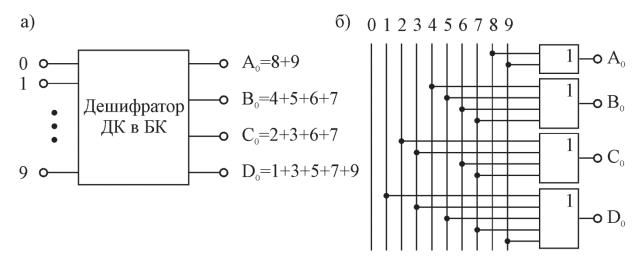

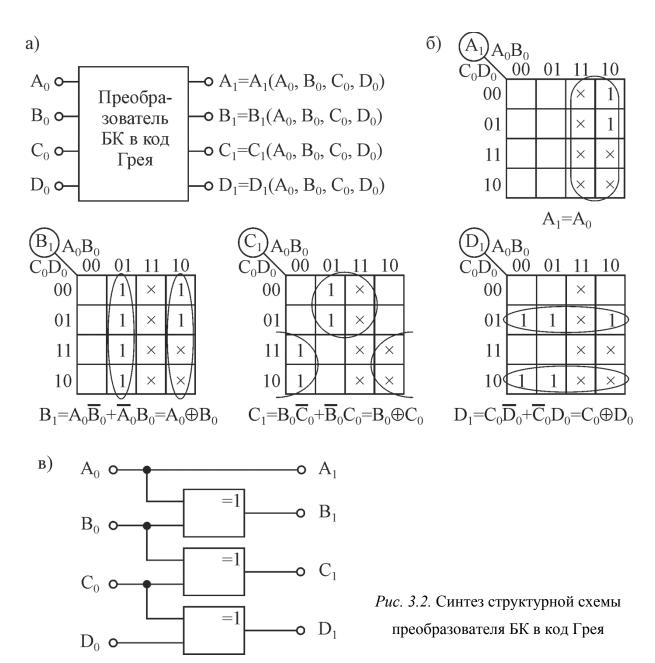

Поскольку шифраторы и дешифраторы являются, вообще говоря, частными случаями преобразователей кодов, общее правило построения этих ЦУ звучит так: синтез ПК осуществляется согласно таблице истинности, в которой разряды исходного кода являются независимыми переменными, а разряды конечного кода — логическими функциями этих переменных. Очевидно, что таблицы истинности для взаимного преобразования рассмотренных числовых кодов нетрудно получить из табл. 3.1. Пример построения структурной схемы шифратора десятичных цифр в БК приведен на рис. 3.1, а синтез преобразователя БК в код Грея — на рис. 3.2.

Таблица 3.1

| Десятичные                | БК (бинарный код)       | Код Грея       | Код +3         | Код Айкена     | Код 2 из 5        | Код Джонсона      |

|---------------------------|-------------------------|----------------|----------------|----------------|-------------------|-------------------|

| пфир                      | $\mathrm{A_0B_0C_0D_0}$ | $A_1B_1C_1D_1$ | $A_2B_2C_2D_2$ | $A_3B_3C_3D_3$ | $A_4B_4C_4D_4E_4$ | $A_5B_5C_5D_5E_5$ |

| 0                         | 0000                    | 0000           | 0 0 1 1        | 0000           | 0 1 1 0 0         | 00000             |

| 1                         | 0 0 0 1                 | 0 0 0 1        | 0 1 0 0        | 0 0 0 1        | 11000             | 10000             |

| 2                         | 0 0 1 0                 | 0 0 1 1        | 0 1 0 1        | 0 0 1 0        | 10100             | 11000             |

| 8                         | 0 0 1 1                 | 0 0 1 0        | 0 1 1 0        | 0 0 1 1        | 10010             | 11100             |

| 4                         | 0 1 0 0                 | 0110           | 0 1 1 1        | 0 1 0 0        | 01010             | 111110            |

| \$                        | 0101                    | 0 1 1 1        | 1000           | 1 0 1 1        | 0 0 1 1 0         | 11111             |

| 9                         | 0 1 1 0                 | 0 1 0 1        | 1001           | 1 1 0 0        | 10001             | 0 1 1 1 1         |

| 7                         | 01111                   | 0100           | 1010           | 1 1 0 1        | 01001             | 0 0 1 1 1         |

| 8                         | 1000                    | 1100           | 1011           | 1 1 1 0        | 00101             | 00011             |

| 6                         | 1001                    | 1 1 0 1        | 1100           | 1111           | 00011             | 00001             |

|                           | 1 0 1 0                 | 1000           | 0000           | 0 1 0 1        |                   |                   |

|                           | 1011                    | 1001           | 0 0 0 1        | 0 1 1 0        |                   |                   |

| Избыточные                | 1100                    | 1010           | 0 0 1 0        | 0 1 1 1        | Остальные         | Остальные         |

| (нештатные)<br>комбинапии | 1101                    | 1 0 1 1        | 1101           | 1000           | 22<br>комбинашии  | 22<br>комбинации  |

|                           | 11110                   | 1110           | 11110          | 1001           |                   |                   |

|                           | 1111                    | 1111           | 1111           | 1010           |                   |                   |

Рис. 3.1. Получение структурной схемы шифратора десятичных цифр в БК

33

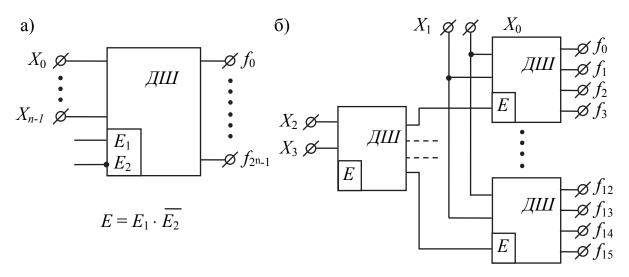

Наконец, несколько слов о дешифраторах. Полным n-разрядным ДШ называется логическая структура К-типа, реализующая все минтермы n входных переменных, т. е. устройство с системой выходных функций

реализуемых на основе операции логического умножения. Полный ДШ (рис. 3.3, а) имеет n логических входов,  $2^n$  выходов, а также один или более входов разрешения работы E (Enable). С точки зрения изготовления ДШ относятся к крайне неудачным схемам, так как при простой внутренней структуре и малом числе схемных ЛЭ имеют много внешних выводов. Для размещения в обычном недорогом корпусе годятся ДШ максимум с четырьмя информационными входами, поэтому более «размерных» ДШ в сериях ИС нет. Для наращивания разрядности ДШ входное слово делится на группы, где разрядность группы младших разрядов соответствует числу входов имеющихся ДШ, а оставшаяся группа старших разрядов служит для получения сигналов E для ДШ младших разрядов. Пример реализации 4-входового ДШ на основе 2-входовых приведен на рис. 3.3, б.

Puc. 3.3

Дешифраторы можно использовать для получения произвольных логических функций. Действительно, на выходах ДШ вырабатываются все минтермы данного числа аргументов, так что собирая нужные минтермы по схеме ИЛИ, можно получить любую функцию.

#### 3.2. Мультиплексоры и демультиплексоры

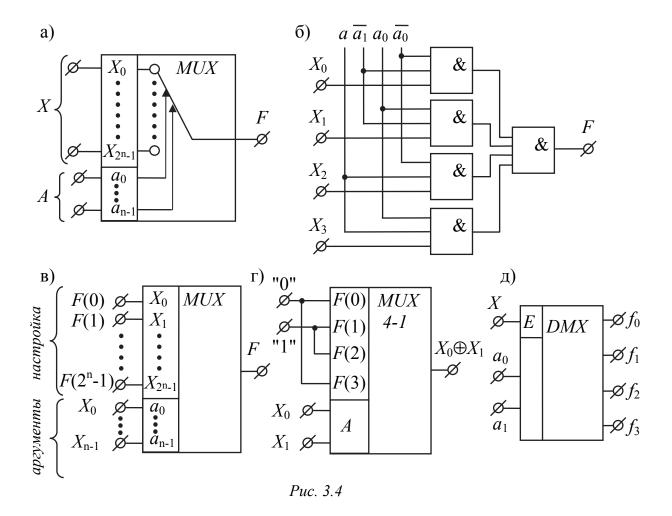

*Мультиплексоры* (Multiplexer, MUX) осуществляют подключение одного их входных каналов к выходу при подаче соответствующего управляющего (адресного) сигнала. Упрощенно работу одноразрядного MUX можно представить с помощью многопозиционного ключа (рис. 3.4, a), где адресный код A задает переключателю определенное положение, соединяя с выходом F один из информационных входов  $X_i$ . Работа MUX описывается мультиплексной формулой

$$F = X_0 \overline{a_{n-1}} \dots \overline{a_1} \overline{a_0} + X_1 \overline{a_{n-1}} \dots \overline{a_1} a_0 + \dots + X_{2^{n-1}} a_{n-1} \dots a_1 a_0,$$

(3.2)

где при любом значении адресного кода все слагаемые, кроме одного, равны нулю.

Реализация MUX на 4 входа на ЛЭ И–НЕ приведена на рис. 3.4, б. В стандартных сериях ИС размерность MUX не более «16–1».

Одной из замечательных возможностей применения МUX является построение на их основе универсальных логических модулей (УЛМ), реализующих (при определенной настройке) любую логическую функцию данного числа аргументов. Для этого достаточно изменить назначение его входов: на адресные входы подавать аргументы функций, а на информационные — сигналы настройки (рис. 3.4, в). При этом каждому набору аргументов на выходе будет соответствовать свой сигнал настройки и, если этот сигнал есть значение функции на данном наборе аргументов, задача решена. Ясно, что разным функциям будут соответствовать разные коды настройки. Пример реализации функции ИСКЛЮЧАЮЩЕЕ ИЛИ с помощью МUХ «4—1» показан на рис. 3.4, г.

Демультиплексоры (DMX) выполняют операцию, обратную MUX — передают данные из одного входного канала в один из каналов — приемников в соответствии с сигналами управления. Нетрудно заметить, что ДШ со входом разрешения E будет работать в режиме DMX, если на вход E подавать информационный сигнал. Действительно, при E=1 адресация ДШ приведет к возбуждению соответствующего выхода, при E=0 — нет, что эквивалентно передаче информационного сигнала в адресованный выходной канал. Условное обозначение ДШ—DMX размерности «1—4» показано на рис. 3.4, д. Многоразрядные DMX составляются из нескольких DMX меньшей разрядности (демультиплексное дерево) подобно ДШ (рис. 3.3, б).

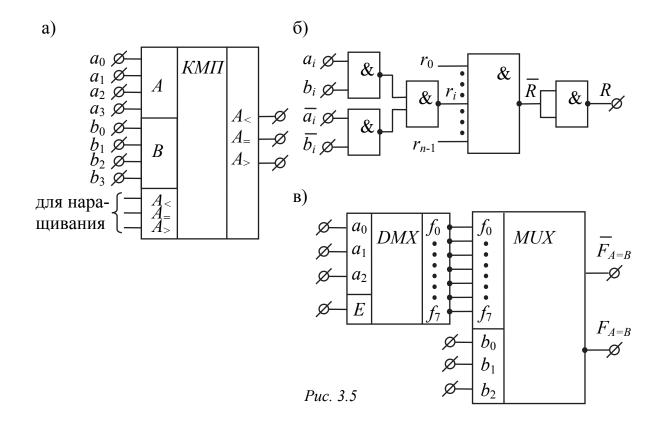

#### 3.3. Компараторы и схемы контроля

Компараторы (устройства сравнения) определяют отношения между двоичными словами, среди которых основными считают «равно» (A = B) и «больше» (A > B). Остальные отношения можно записать как

$$F_{A \neq B} = \overline{F}_{A=B}; \quad F_{A < B} = F_{B > A}; \quad F_{A \ge B} = \overline{F}_{B > A}; \quad F_{A \le B} = \overline{F}_{A > B}.$$

(3.3)

В сериях ИС цифровых элементов обычно имеются компараторы (КМП) с тремя выходами: «равно», «больше» и «меньше» (рис. 3.5, а). КМП на равенство строятся на основе поразрядных операций над одноименными разрядами обоих слов, поскольку слова равны при равенстве их одноименных разрядов. Признак равенства разрядов выражается функцией эквивалентности ( $f_9$ , табл. 1.2)

$$r_i = a_i b_i + \overline{a_i} \, \overline{b_i} = \overline{a_i \oplus b_i} \,, \tag{3.4}$$

а признак равенства слов  $R=r_{n-1}...r_1r_0$ .

Варианты реализации КМП на равенство на основе ЛЭ И–НЕ, MUX и DMX приведены на рис. 3.5, б, в соответственно.

Построение КМП на «больше» для одноразрядных слов требует реализации функции  $F_{A>B} = a\overline{b}$  ( $f_2$ , табл. 1.2). Для многоразрядных слов эту функцию можно получить следующим рассуждением — если старшие разряды  $a_{n-1}$  и  $b_{n-1}$  не равны, то результат известен независимо от младших, т.е. к анализу следующего разряда нужно переходить только при равенстве предыдущих. В общем случае для n-разрядных слов имеем

$$F_{A>B} = a_{n-1}\overline{b}_{n-1} + r_{n-1}a_{n-2}\overline{b}_{n-2} + \dots + r_{n-1}r_{n-2}\dots r_1a_0\overline{b}_0.$$

(3.5)

Компараторы для слов большой разрядности получают наращиванием размерности обычным путем, с использованием нескольких ИС КМП.

Передача и обработка информации ЦУ сопровождается ошибками, возникающими из-за действия помех. Во многих случаях исключение ошибок является жизненно важной задачей, при решении которой цели контроля могут быть разными:

- 1. *Предотвращение ошибок* путем применения высококачественных элементов, исключения влияния окружающей среды и т.п., что, впрочем, не гарантирует полного избавления от них.

- 2. Выявление (поскольку они неизбежны) и исправление (маскирование) ошибок за счет введения избыточности.

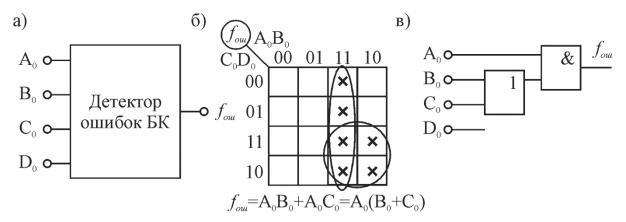

Одним из простейших способов обнаружения ошибок является использование избыточных комбинаций. Например, формируя функцию ошибок  $f_{out}$  бинарного кода (табл. 3.1) как сумму избыточных комбинаций  $f_{out} = A_0(B_0 + C_0)$ , можно с помощью дополнительной структуры детектора (рис. 3.6) фиксировать ошибки в работе старших разрядов. Обнаружение всех единичных сбоев при обработке числовой информации возможно только при использовании 5-разрядных кодов (2 из 5, табл. 3.1), обнаружение, а тем более исправление ошибок более высокой кратности требуют дальнейшего увеличения схемной избыточности ЦУ.

Рис. 3.6. Определение структурной схемы детектора ошибок БК

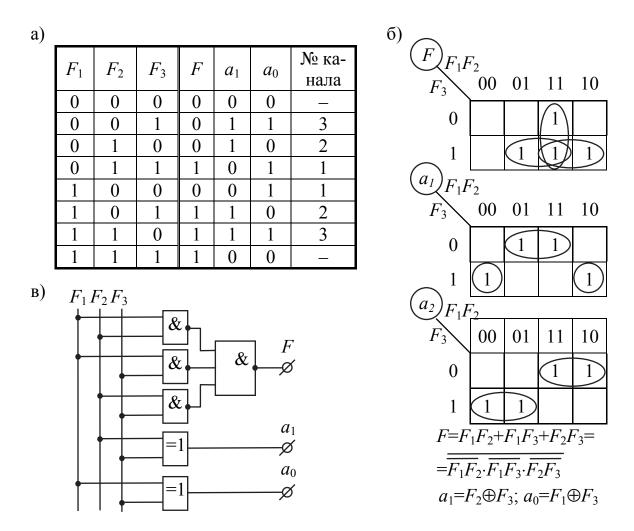

Один из возможных путей маскирования — использование трех (пяти) кратного резервирования с выработкой выходного сигнала путем «голосования» с помощью *мажоритарных элементов* (МЭ), когда ошибка в одном (двух) каналах не влияет на конечный результат. Пример построения одноразрядного МЭ на 3 входа приведен на рис. 3.7, где согласно таблице истинности а) схема в) вырабатывает выходной сигнал F по большинству «голосов» из  $F_1$ ,  $F_2$ ,  $F_3$ , а разряды  $a_1$ ,  $a_0$  показывают номер канала, где появилась ошибка. Исправление 2-кратных ошибок требует 5-кратного резервирования с использованием МЭ на 5 входов. Для контроля многоразрядных слов рассмотренные МЭ ставятся в каждый разряд. Заметим, что в схемах типа рис. 3.7 от МЭ требуется особенно высокая надежность, так как их отказы делают бесполезной всю схему резервирования.

Достаточно простым и широко применяемым методом выявления ошибок является контроль по модулю 2 (по четности/нечетности). Из теории кодирования известно [7], что условие обнаружения и исправления ошибок при использовании кодов имеет вид

$$d_{min} = 2k_{ucnp} + k_{o6H} + 1, (3.6)$$

где  $d_{min}$  — минимальное кодовое расстояние;  $k_{oбh}$ ,  $k_{ucnp}$  — кратность обнаруживаемых и исправляемых ошибок соответственно.

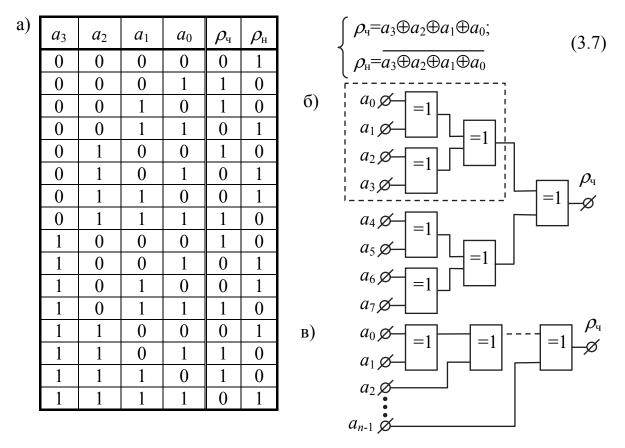

*Рис. 3.7.* Процедура определения структурной схемы одноразрядного мажоритарного элемента при использовании трехкратного резервирования

Обычный БК имеет  $d_{min} = 1$ , поэтому для обнаружения всех единичных ошибок необходимо увеличить  $d_{min}$  на 1, что и сделано в коде контроля по модулю 2 (рис. 3.8, а), когда каждое слово  $a_3a_2a_1a_0$  дополняется контрольным разрядом, значение которого выбирается так, чтобы сделать четным ( $\rho_{\rm H}$ ) или нечетным ( $\rho_{\rm H}$ ) вес каждой кодовой комбинации. При одиночной ошибке четность (нечетность) веса слова меняется, что легко обнаруживается схемами контроля. Логические возможности обеих форм контроля одинаковы, некоторые преимущества той или иной формы могут проявляться при технической реализации.

Puc. 3.8

Из таблицы истинности рис. 3.8, а нетрудно получить выражения для  $\rho_{\rm q}$  (3.7), которые реализуются *схемами свертки* пирамидального (рис. 3.8, б) или последовательного (рис. 3.8, в) типа. Очевидно, что контроль по модулю 2 эффективен там, где вероятность единичной ошибки много больше, чем вероятность двойной. Развитие этой идеи находит свое отражение в кодах Хемминга, где добавление большего числа контрольных разрядов позволяет не только обнаруживать, но и исправлять единичные или двойные ошибки.

#### 3.4. Сумматоры

Основной арифметической операцией является операция сложения чисел, поскольку остальные (вычитание, умножение, деление) могут быть выполнены на ее основе. Для арифметического сложения чисел в ЦУ служат разнообразные сумматоры, среди которых можно выделить основные типы:

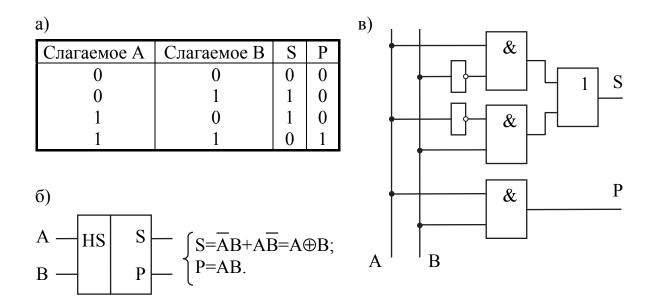

1. Одноразрядный полусумматор — для сложения 2-х двоичных цифр A, B с образованием суммы S и переноса P в следующий разряд (рис. 3.9).

Рис. 3.9. Построение структурной схемы одноразрядного полусумматора

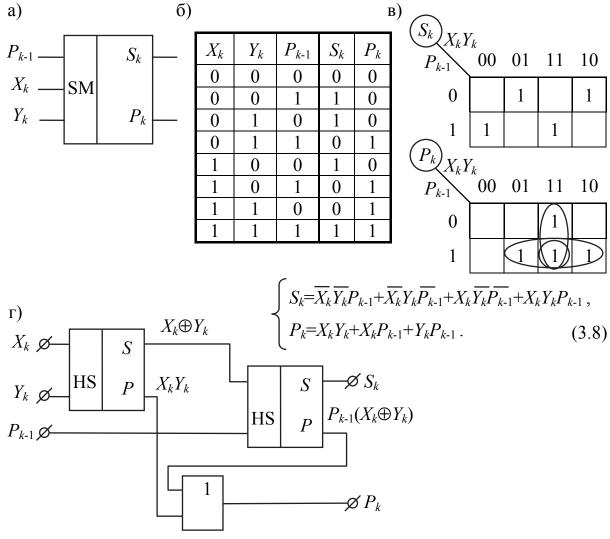

2. Одноразрядный сумматор — для сложения трех двоичных (два слагаемых + перенос из предыдущего разряда) цифр  $X_k$ ,  $Y_k$ ,  $P_{k-1}$  с образованием суммы  $S_k$  и переноса  $P_k$  (рис. 3.10), где выражение (3.8) можно упростить, если воспользоваться  $\overline{P}_k$  в качестве вспомогательного аргумента

$$\begin{cases}

S_k = (X_k + Y_k + P_{k-1})\overline{P_k} + X_k Y_k P_{k-1}, \\

P_k = X_k Y_k + X_k P_{k-1} + Y_k P_{k-1},

\end{cases}$$

(3.9)

что определит структуру так называемого «минимального» сумматора. Если же представить выражение (3.8) в виде

$$\begin{cases}

S_k = X_k \oplus Y_k \oplus P_{k-1}, \\

P_k = X_k Y_k + P_{k-1} (X_k \oplus Y_k),

\end{cases}$$

(3.10)

то рассматриваемый сумматор можно реализовать на основе двух схем полусумматоров (рис. 3.10,  $\Gamma$ ).

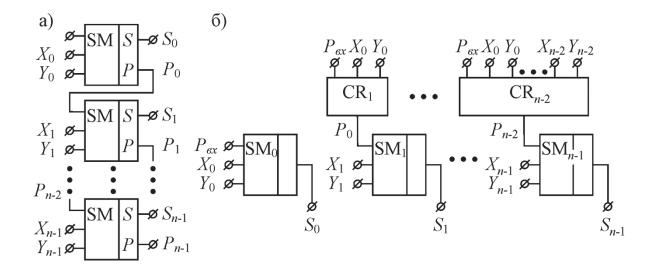

3. Параллельный сумматор с последовательным переносом — это цепочка одноразрядных сумматоров, соединенных последовательно по цепям переноса (рис. 3.11, а). Время суммирования для такого n-разрядного сумматора пропорционально числу разрядов и в наихудшем случае составляет  $t_{SM}$ = $(n+1)\tau_3$ , где  $\tau_3$  — усредненное время задержки ЛЭ, реализующих одноразрядный сумматор.

*Puc. 3.10.* Определение структурной схемы одноразрядного комбинационного сумматора

4. Параллельный сумматор с параллельным переносом — суммирующее ЦУ, в котором результаты во всех разрядах вырабатываются одновременно, параллельно во времени, что обеспечивает максимальное быстродействие ( $t_{SM}$ =4—5  $\tau_3$ ). Структура такого сумматора приведена на рис. 3.11, б, где  $P_{ex}$  — внешний входной перенос, внутренние переносы  $P_k$  формируются дополнительными схемами  $CR_k$  (от саггу), а поразрядные сумматоры  $SM_k$  предельно упрощены, поскольку выхода P от них не требуется.

*Рис. 3.11.* Структурные схемы многоразрядных сумматоров с последовательным (а) и параллельным (б) переносом

Для определения структуры  $CR_k$  введем две вспомогательные функции — функцию генерации  $g_k = X_k Y_k$ , равную «1», если перенос  $P_k$  появляется независимо от входного переноса  $P_{k-1}$ , и функцию прозрачности (транзита)  $h_k = X_k + Y_k$ , которая равна «1», если перенос  $P_k$  появляется только при  $P_{k-1} =$  «1». Теперь выражение для сигнала переноса можно записать в виде  $P_k = g_k + h_k P_{k-1}$ , поразрядное применение которого позволяет получить выходные функции  $CR_k$ :

$$\begin{cases}

P_{0} = g_{0} + P_{ex}h_{0}, \\

P_{1} = g_{1} + P_{0}h_{1} = g_{1} + g_{0}h_{1} + P_{ex}h_{1}h_{0}, \\

\dots \\

P_{k} = g_{k} + g_{k-1}h_{k} + g_{k-2}h_{k}h_{k-1} + \dots + g_{0}h_{k} \dots h_{1} + P_{ex}h_{k} \dots h_{0}.

\end{cases} (3.11)$$

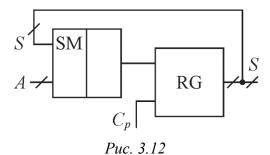

5. *Накапливающий сумматор (аккумулятор)* – сочетание комбинационного сумматора и регистра (рис. 3.12), работающего по формуле

S = S + A, согласно которой к содержимому SM добавляется очередное слагаемое и S результат замещает старое значение суммы. Очередное прибавление A тактируется синхроимпульсами  $C_p$ .

#### 3.5. Арифметико-логические

#### устройства и матричные умножители

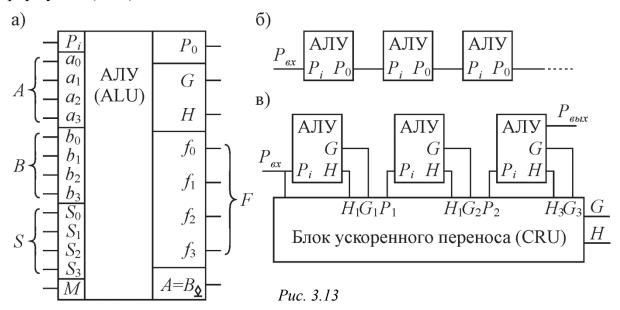

Арифметико-логические устройства (АЛУ) (рис. 3.13, а) выполняют над двоичными словами A, B ряд операций, представленных в табл. 3.2, где сигнал M задает тип выполняемых операций, двоичные сигналы S (для простоты указаны их десятичные эквиваленты) определяют выполняемую операцию, а  $P_i$  означает входной перенос. Результаты операций вырабатываются на выходах F, выходы G и H дают функции генерации и прозрачности, используемые для параллельных переносов при наращивании размерности АЛУ, вход  $P_i$  служит для подачи  $P_{ex}$ , сигнал  $P_0$  определяет выходной перенос, а выход A = B (с открытым коллектором) реализует функцию сравнения на равенство, 16 логических операций (M = 1) позволяют воспроизводить все функции двух переменных, в арифметико-логических (M = 0) сначала выполняются логические операции (в скобках), а затем полученные числа складываются арифметически.

При работе со словами большой размерности АЛУ соединяют друг с другом с организацией последовательных (рис. 3.13, б) или параллельных (рис. 3.13, в) переносов. Во втором случае совместно с АЛУ применяют блоки ускоренного переноса (*CRU*), вырабатывающие сигналы переноса по формулам (3.11).

Таблица 3.2

Необходимость увеличения скорости вычислений обусловила появление специальных множительных устройств - матричных умножителей, структура которых тесно связана со структурой математических выражений для операции умножения. Например, при перемножении двоичных чисел  $A_m = a_{m-1}...a_1a_0$  и  $B_n =$  $=b_{n-1}...b_1b_0$  по обычной схеме «умножения столбиком» (см. рис. 3.14 для m = n = 3) произведение выразится числом  $Z_{m+n} = z_{m+n-1}z_{m+n-2}...z_1z_0$ , где  $z_i$  определяются суммированием частичных произведений  $a_i b_i$ , которые могут вырабатываться параллельно во времени конъюнкторами. Развитием множительных (МБ) являются множительно-суммирующие блоки (МСБ), [13]

|    | Логические                  | Арифметико-                          |

|----|-----------------------------|--------------------------------------|

| S  | функции                     | логические                           |

|    | (M=1)                       | функции (М=0)                        |

| 0  | $\overline{\overline{A}}$   | $A+P_{ex}$                           |

| 1  | <del>A+B</del>              | $(A+B)+P_{ex}$                       |

| 2  | ĀB                          | $(A+\overline{B})+P_{ex}$            |

| 3  | 0                           | $1+P_{ex}$                           |

| 4  | ĀB                          | $A + (A\overline{B}) + P_{ex}$       |

| 5  | $\overline{\mathrm{B}}$     | $(A+B)+(A\overline{B})+P_{ex}$       |

| 6  | A⊕B                         | $A + \overline{B} + P_{ex}$          |

| 7  | $A\overline{\overline{B}}$  | $(A\overline{B}) + 1 + P_{ex}$       |

| 8  | Ā+B                         | $A + (AB) + P_{ex}$                  |

| 9  | $\overline{A \oplus B}$     | $A+B+P_{ex}$                         |

| 10 | В                           | $(A + \overline{B}) + (AB) + P_{ex}$ |

| 11 | AB                          | $(AB)+1+P_{ex}$                      |

| 12 | 1                           | $A+A+P_{ex}$                         |

| 13 | $A+\overline{\overline{B}}$ | $(A+B)+A+P_{ex}$                     |

| 14 | A+B                         | $(A + \overline{B}) + A + P_{ex}$    |

| 15 | A                           | $A+1+P_{ex}$                         |

выполняющие операцию  $Z = A_m \times B_n + C_m + D_n$  и требующие для реализации  $(m \times n)$  конъюнкторов и  $(m \times n)$  одноразрядных сумматоров. Изложенное показывает, что основную задержку в процесс выработки произведения вносит суммирование частичных произведений  $a_i b_i$ . Для уменьшения

$$\begin{array}{c}

\times \begin{array}{c}

a_2 a_1 a_0 \\

b_2 b_1 b_0

\end{array} \\

+ a_2 b_1 a_1 b_1 a_0 b_1 \\

+ a_2 b_2 a_1 b_2 a_0 b_2

\end{array}$$

$$Z_5 Z_4 Z_3 Z_2 Z_1 Z_0$$

Puc. 3.14

их числа используют специальные алгоритмы, например, модифицированный алгоритм Бута (умножения на два разряда сразу), который позволяет

разреживать спектр частичных произведений (оставляя только четные или только нечетные), почти вдвое сокращая время получения результата.

Разработке МБ и МСБ уделяют внимание многие фирмы. В отечественной серии КМОП (1802) представлены умножители 8×8, 12×12, 16×16 (ВРЗ, ВР4, ВР5 соответственно), в схемотехнике ЭСЛ – 1800ВР1 (8×8 за 17 нс). Зарубежные фирмы (Motorola, ВІТ, Hitachi) выпускают умножители размерностью 16×16 и выше с временами умножения 3–5 нс.

#### 3.6. Контрольные задания по проектированию К-устройств

3.6.1. Используя теорему де Моргана, реализовать в указанной элементной базе минимальную комбинационную структуру с законом функционирования f(A,B,C,D) (номера вариантов приведены в табл. 3.3):

Таблица 3.3

| Логическая функция $f(A,B,C,D)$                                                                                                 | Элемент | ная база |

|---------------------------------------------------------------------------------------------------------------------------------|---------|----------|

| логическая функция ј (А,Б,С,Б)                                                                                                  | И–НЕ    | ИЛИ–НЕ   |

| $\overline{BD} + \overline{B}CD + AC\overline{D} + AB\overline{C}\overline{D}$                                                  | 1       | 13       |

| $\overline{BC} + \overline{BCD} + \overline{BCD} + \overline{ABCD}$                                                             | 2       | 14       |

| $\overline{\overline{C}}\overline{D} + \overline{A}BD + \overline{A}C\overline{D} + A\overline{B}C\overline{D}$                 | 3       | 15       |

| $\overline{CD} + \overline{BC}\overline{D} + ABD + \overline{A}BCD$                                                             | 4       | 16       |

| $\overline{A}\overline{B} + \overline{A}B\overline{D} + A\overline{C}\overline{D} + A\overline{B}D + AC\overline{D}$            | 5       | 17       |

| $\overline{A}D + \overline{A}\overline{B}\overline{D} + \overline{B}\overline{C}\overline{D} + ABD + \overline{B}C\overline{D}$ | 6       | 18       |

| $AB + \overline{A}BC + \overline{B}CD + \overline{A}B\overline{C}D$                                                             | 7       | 19       |

| $\overline{AB} + AB\overline{C} + AB\overline{D} + \overline{AB}CD$                                                             | 8       | 20       |

| $\overline{A}\overline{B} + BD + A\overline{B}\overline{C} + A\overline{B}C + \overline{A}BC\overline{D}$                       | 9       | 21       |

| $\overline{CD} + \overline{AB}\overline{C} + \overline{ABC} + \overline{ABC}D + ABCD$                                           | 10      | 22       |

| $\overline{BD} + BC + \overline{A}BD + AC\overline{D} + AB\overline{C}D$                                                        | 11      | 23       |

| $\overline{AB}+BC+\overline{CD}+\overline{AD}$                                                                                  | 12      | 24       |

- 3.6.2. Определить минимальную структуру шифратора ДК: а) в код Грея; б) в код Айкена; в) в код +3; г) в код 2 из 5; д) в код Джонсона.

- 3.6.3. Построить простейшую структуру детектора ошибок кода N, использующую нештатные (избыточные) комбинации (варианты заданий представлены табл. 3.4):

Таблица 3.4

| Ко         | дΝ     | Грея | Айкена | +2 | +3 | +4 | +6 | +7 | +8 | +10 | +12 | +14 | +15 |

|------------|--------|------|--------|----|----|----|----|----|----|-----|-----|-----|-----|

| ія база    | И-НЕ   | 1    | 2      | 3  | 4  | 5  | 6  | 7  | 8  | 9   | 10  | 11  | 12  |

| Элементная | или-не | 13   | 14     | 15 | 16 | 17 | 18 | 19 | 20 | 21  | 22  | 23  | 24  |

<u>Примечание.</u> Коды +2, +4, +6,... образуются из БК по тому же принципу, что и код +3, т.е. сдвигом начальной кодовой комбинации на указанное число.

3.6.4. Синтезировать оптимальную структурную схему преобразователя кода  $N_1$  в код  $N_2$ , используя для минимизации логических выражений избыточные комбинации (номера вариантов указаны в табл. 3.5).

Таблица 3.5

|                                          |    |      |        |    |        | * 0 11 11 2 11 0 11 |

|------------------------------------------|----|------|--------|----|--------|---------------------|

| Код N <sub>2</sub><br>Код N <sub>1</sub> | БК | Грея | Айкена | +3 | 2 из 5 | Джонсона            |

| БК                                       |    | 1    | 2      | 3  | 4      | 5                   |

| Грея                                     | 6  | _    | 7      | 8  | 9      | 10                  |

| Айкена                                   | 11 | 12   | _      | 13 | 14     | 15                  |

| +3                                       | 16 | 17   | 18     |    | 19     | 20                  |

| +5                                       | 21 | 22   | 23     | 24 | _      | 25                  |

| +9                                       | 26 | 27   | 28     | 29 | 30     | _                   |

3.6.5. С помощью мультиплексора «4–1» (рис. 3.4, г) реализовать заданную логическую функцию f(X,Y) (табл. 3.6):

Таблица 3.6

| № варианта | 1   | 2  | 3 | 4  | 5   | 6                | 7                               | 8                       | 9                | 10              | 11                | 12              |

|------------|-----|----|---|----|-----|------------------|---------------------------------|-------------------------|------------------|-----------------|-------------------|-----------------|

| f(X,Y)     | «1» | XY | X | XY | X+Y | $\overline{X+Y}$ | $XY + \overline{X}\overline{Y}$ | $\overline{\mathbf{Y}}$ | $X+\overline{Y}$ | $X\overline{Y}$ | $\overline{X}$ +Y | $\overline{XY}$ |

#### Контрольные вопросы

- 1. Какие цифровые коды допускают прямую реализацию операции сравнения?

- 2. Какова должна быть минимальная дистанция кода, позволяющего обнаруживать все единичные ошибки во всех разрядах?

- 3. Сколько дешифраторов с 4 информационными входами необходимо для реализации ДШ на 8 входов?

- 4. Можно ли получить произвольную логическую функцию с помощью ДШ? Если «да», то каким образом?

- 5. Может ли ДШ работать в режиме демультиплексора? Если «да», то при каком условии?

- 6. Что необходимо для реализации универсального логического модуля на основе мультиплексора?

- 7. Из таблицы истинности рис. 3.8 а получить выражения для функций четности  $\rho_{_{\!\mathit{H}}}$  и нечетности  $\rho_{_{\!\mathit{H}}}$  кода контроля по модулю 2.

- 8. Почему при построении схем свертки чаще используют пирамидальные структуры?

- 9. В каких случаях для обнаружения ошибок эффективен контроль по модулю 2?

- 10. Используя  $P_{\kappa}$  в качестве вспомогательного аргумента, получите выражения (3.10) для структуры «минимального» сумматора.

- 11. Как выглядит структура параллельного сумматора с последовательным переносом?

- 12. С какой целью и каким образом организуют параллельный перенос в многоразрядных сумматорах?

- 13. Какие методы организации арифметической операции вычитания двоичных чисел Вы знаете?

- 14. Зачем в структуре выходов АЛУ предусмотрена реализация функций генерации G и прозрачности H?

- 15. Какая операция определяет быстродействие матричных умножителей? На чем базируются алгоритмы ускоренного умножения?

## ЗАДАНИЯ ДЛЯ САМОСТОЯТЕЛЬНОГО ПРОЕКТИРОВАНИЯ ЦИФРОВЫХ АВТОМАТОВ К-ТИПА

Выполнение самостоятельных заданий по построению ЦУ с заданными свойствами производится по обычной схеме: таблица истинности  $\rightarrow$  карты минтермов  $\rightarrow$  выходные функции в виде СДНФ или ДНФ  $\rightarrow$  структурная схема – для устройств К-типа, граф переходов  $\rightarrow$  разностные картыминтермов  $\rightarrow$  прикладные + характеристические уравнения  $\rightarrow$  уравнения входов  $\rightarrow$  структурная схема – для устройств П-типа. При этом обязателен параллельный обзор вариантов для получения оптимального решения. Отчет о выполненной работе должен содержать основные этапы проектирования и обсуждение полученных результатов.

К.1. На основе ДШ с m входами реализовать структурную схему ДШ с n входами (номера вариантов см. в табл. К.1):

Таблица К.1

| m $n$ | 3 | 4 | 5  | 6  | 7  | 8  |

|-------|---|---|----|----|----|----|

| 2     | 1 |   | 2  | 3  | 4  | 5  |

| 3     | _ | 6 | 7  | 8  | 9  | 10 |

| 4     | _ | _ | 11 | 12 | 13 | 14 |

К.2. Определить структурную схему ДШ для:

- семисегментного индикатора (рис. 2.9, б), допускающего визуализацию слов

- а) ГОЛОВА, НОГА;

- б) РУБЛЬ, ЕВРО;